雙列直插封裝

Clash Royale CLAN TAG#URR8PPP

Clash Royale CLAN TAG#URR8PPP

三個14針(DIP14)的DIP包裝IC

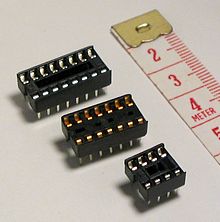

16針、14針及8針的DIP插座(socket)

雙列直插封裝(英语:dual in-line package) 也稱為DIP封裝或DIP包裝,簡稱為DIP或DIL[1],是一種積體電路的封裝方式,積體電路的外形為長方形,在其兩側則有兩排平行的金屬引脚,稱為排針。DIP包裝的元件可以焊接在印刷電路板電鍍的貫穿孔中,或是插入在DIP插座(socket)上。

DIP包裝的元件一般會簡稱為DIPn,其中n是引脚的個數,例如十四針的積體電路即稱為DIP14,右圖即為DIP14的積體電路。

目录

1 應用

1.1 使用

1.2 安裝方式

2 結構

3 引脚數及間距

4 方向和接腳編號

5 其他衍生的封裝

6 相關條目

7 參考資料

應用

一個放在麵包板上的電路,其中包括四個DIP的IC、左上方及左下方分別是DIP的條狀顯示器及七段顯示器

積體電路常使用DIP包裝,其他常用DIP包裝的零件包括DIP開關、LED、七段顯示器、條狀顯示器及繼電器。電腦及其他電子設備的排線也常用DIP包裝的接頭。

使用

最早的DIP包裝元件是由快捷半導體公司的Bryant Buck Rogers在1964年時發明,第一個元件有14個接腳,相當類似今天的DIP包裝元件[2]。其外形為長方形,相較於更早期的圓形元件,長方形元件可以提高電路板中元件的密度[3]。DIP包裝的元件也很適合自動化裝配設備,電路板上可以有數十個到數百個IC,利用波峰焊接機焊接所有零件,再由自動測試設備進行測試,只需要少數的人工作業。DIP元件的大小其實比其內部的積體電路大很多。在二十世紀末時表面黏著技術(SMT)包裝的元件可以縮小系統的體積及重量。不過有些場合仍會用到DIP元件,例如在製作電路原型時,就會使用DIP元件配合麵包板製作電路原型,方便元件的插入及移除。

DIP包裝元件是1970及1980年代微電子產業的主流。在21世紀初的使用量逐漸減少,被像是PLCC及SOIC等表面黏著技術的封裝所取代。表面黏著技術元件的特性適合量產時使用,但在電路原型製作時比較不便。由於有些新的元件只提供表面黏著技術封裝的產品,因此有許多公司生產將SMD元件轉換為DIP包裝的轉接器,可以將表面黏著技術封裝的IC放在轉接器中,像DIP包裝元件一様的再接到麵包板或其他配合直插式元件的電路原形板(像洞洞板)中。

對於像EPROM或是GAL之類的可編程元件而言,DIP封裝的元件由於方便由外部燒錄設備燒錄資料(DIP封裝元件可以直接插入燒錄設備對應的DIP插座),仍盛行了一段時間。不過隨著在線燒錄(ISP)技術的普及,DIP封裝元件方便燒錄的好處也就不再重要。在1990年代,超過20隻接腳的元件可能還有DIP封裝的產品。而二十一世紀時,許多新的可編程元件已都是SMT封裝,不再提供DIP封裝的產品。

安裝方式

DIP封裝元件可以用通孔插装技术的方式安裝在電路板上,也可以利用DIP插座安裝。利用DIP插座可以方便元件的更換,也可以避免在焊接時造成元件過熱的情形。一般插座會配合體積較大或是單價較高的積體電路使用。像測試設備或燒錄器等,常常需要安裝及拆下積體電路的場合,會使用零抗力的插座。DIP封裝元件也可以配合麵包板使用,麵包板一般是作為教學、開發設計或元件設計而使用。

結構

雙列直插封裝晶片的剖面圖

雙列直插封裝晶片的封裝一般是由塑膠或陶瓷製成。陶瓷封裝的氣密性良好,常用在需要高可靠度的設備。不過大部份的雙列直插封裝晶片都是使用熱固性樹脂塑膠。一個不到2分鐘的固化週期,可以生產上百個的晶片。

引脚數及間距

常用的DIP封裝符合JEDEC標準,二引脚之間的間距(脚距)為0.1吋(2.54毫米)。二排引脚之間的距離(行間距、row spacing)則依引脚數而定,最常見的是0.3吋(7.62毫米)或0.6吋(15.24毫米)。其他較少見的距離有0.4吋(10.16毫米)或0.9吋(22.86毫米),也有一些包裝是脚距0.07吋(1.778毫米),行間距則為0.3吋、0.6吋或0.75吋。

前蘇聯及東歐國家使用的DIP封裝大致接近JEDEC標準,但腳距使用公制的2.5毫米,而不是來自英制的0.1吋(2.54毫米)。

DIP封裝的引脚數恆為偶數。若行間距為0.3吋,常見的引脚數為8至24,偶爾也會看到引脚數為4或28的包裝。若行間距為0.6吋,常見的引脚數為24、28、32或40,也有引脚數為36、48或52的包裝。摩托羅拉 68000及Zilog Z180等CPU的引脚數為64,這是常用DIP封裝的最大引脚數[4]。

方向和接腳編號

接腳以逆時針的順序編號

如右圖所示,當元件的識別缺口朝上時,左側最上方的接腳為接腳1,其他接腳則以逆時針的順序依序編號。有時接腳1也會以圓點作為標示。

例如DIP14的IC,識別缺口朝上時,左側的接腳由上往下依序為接腳1至7,而右側的接腳由下往上依序為接腳8至14。

其他衍生的封裝

SOIC(Small Outline IC)是一種很常用的表面黏著技術封裝方式,特別常在消費性電子及個人電腦中使用。SOIC可視為是標準IC的PDIP封裝的縮小版,其排針也是在元件的二側。而SOJ(Small Outline J-lead)及SOP(Small Outline Package)系列的封裝方式也是和DIP封裝類似的表面黏著技術封裝方式。

相關條目

- 插針網格陣列

- DIP開關

參考資料

^ see for instance

^ Dummer, G.W.A. Electronic Inventions and Discoveries 2nd ed. Pergamon Press ISBN 0-08-022730-9

^ http://www.computerhistory.org/semiconductor/timeline/1965-Package.html Computer Museum retrieved April 16, 2008

^ Kang, Sung-Mo; Leblebici, Yusuf. CMOS digital integrated circuits (3rd Edition). McGraw-Hill. 2002: 42. ISBN 0072460539. 引文使用过时参数coauthors (帮助)